CY8C20236A Designing with PSoC Designer

The development process for the PSoC device differs from that

of a traditional fixed function microprocessor. The configurable

analog and digital hardware blocks give the PSoC architecture a

unique flexibility that pays dividends in managing specification

change during development and by lowering inventory costs.

These configurable resources, called PSoC Blocks, have the

ability to implement a wide variety of user-selectable functions.

The PSoC development process can be summarized in the

following four steps:

1. Select User Modules

2. Configure User Modules

3. Organize and Connect

4. Generate, Verify, and Debug

Select Components

PSoC Designer provides a library of pre-built, pre-tested

hardware peripheral components called "user modules." User

modules make selecting and implementing peripheral devices,

both analog and digital, simple.

Configure Components

Each of the User Modules you select establishes the basic

register settings that implement the selected function. They also

provide parameters and properties that allow you to tailor their

precise configuration to your particular application. For example,

a PWM User Module configures one or more

digital PSoC blocks, one for each 8 bits of resolution. The user

module parameters permit you to establish the pulse width and

duty cycle. Configure the parameters and properties to correspond to your chosen application. Enter values directly or by

selecting values from drop-down menus. All the user modules

are documented in datasheets that may be viewed directly in

PSoC Designer or on the Cypress website. These user module

datasheets explain the internal operation of the User Module and

provide performance specifications. Each datasheet describes

the use of each user module parameter, and other information

you may need to successfully implement your design.

Organize and Connect

You build signal chains at the chip level by interconnecting user

modules to each other and the I/O pins. You perform the

selection, configuration, and routing so that you have complete

control over all on-chip resources.

Generate, Verify, and Debug

When you are ready to test the hardware configuration or move

on to developing code for the project, you perform the "Generate

Configuration Files" step. This causes PSoC Designer to

generate source code that automatically configures the device to

your specification and provides the software for the system. The

generated code provides application programming interfaces

(APIs) with high-level functions to control and respond to

hardware events at run time and interrupt service routines that

you can adapt as needed.

A complete code development environment allows you to

develop and customize your applications in C, assembly

language, or both.

The last step in the development process takes place inside

PSoC Designer's Debugger (access by clicking the Connect

icon). PSoC Designer downloads the HEX image to the ICE

where it runs at full speed. PSoC Designer debugging capabilities rival those of systems costing many times more. In addition

to traditional single-step, run-to-breakpoint and watch-variable

features, the debug interface provides a large trace buffer and

allows you to define complex breakpoint events that include

monitoring address and data bus values, memory locations and

external signals.

2012年10月26日星期五

CY8C20236A Additional System Resources

CY8C20236A Additional System Resources

System resources provide additional capability, such as I

2

C

slave, SPI master, or SPI slave interfaces, three 16-bit

programmable timers, and various system resets supported by

the M8C.

These system resources provide additional capability useful to

complete systems. Additional resources include low voltage

detection and power on reset. The merits of each system

resource are listed here:

■ The I

2

C slave/SPI master-slave module provides 50/100/400

kHz communication over two wires. SPI communication over

three or four wires runs at speeds of 46.9 kHz to 3 MHz (lower

for a slower system clock).

■ The I

2

C hardware address recognition feature reduces the

already low power consumption by eliminating the need for

CPU intervention until a packet addressed to the target device

is received.

■ The I

2

C enhanced slave interface appears as a 32-byte RAM

buffer to the external I

2

C master. Using a simple predefined

protocol, the master controls the read and write pointers into

the RAM. When this method is enabled, the slave does not stall

the bus when receiving data bytes in active mode. For usage

details, refer to the application note I2C Enhanced Slave

Operation - AN56007.

■ Low-voltage detection (LVD) interrupts can signal the

application of falling voltage levels, while the advanced poweron-reset (POR) circuit eliminates the need for a system

supervisor.

■ An internal reference provides an absolute reference for

capacitive sensing.

■ A register-controlled bypass mode allows the user to disable

the LDO regulator.

System resources provide additional capability, such as I

2

C

slave, SPI master, or SPI slave interfaces, three 16-bit

programmable timers, and various system resets supported by

the M8C.

These system resources provide additional capability useful to

complete systems. Additional resources include low voltage

detection and power on reset. The merits of each system

resource are listed here:

■ The I

2

C slave/SPI master-slave module provides 50/100/400

kHz communication over two wires. SPI communication over

three or four wires runs at speeds of 46.9 kHz to 3 MHz (lower

for a slower system clock).

■ The I

2

C hardware address recognition feature reduces the

already low power consumption by eliminating the need for

CPU intervention until a packet addressed to the target device

is received.

■ The I

2

C enhanced slave interface appears as a 32-byte RAM

buffer to the external I

2

C master. Using a simple predefined

protocol, the master controls the read and write pointers into

the RAM. When this method is enabled, the slave does not stall

the bus when receiving data bytes in active mode. For usage

details, refer to the application note I2C Enhanced Slave

Operation - AN56007.

■ Low-voltage detection (LVD) interrupts can signal the

application of falling voltage levels, while the advanced poweron-reset (POR) circuit eliminates the need for a system

supervisor.

■ An internal reference provides an absolute reference for

capacitive sensing.

■ A register-controlled bypass mode allows the user to disable

the LDO regulator.

CY8C20236A CapSense System

CY8C20236A CapSense System

The analog system contains the capacitive sensing hardware.

Several hardware algorithms are supported. This hardware

performs capacitive sensing and scanning without requiring

external components. The analog system is composed of the

CapSense PSoC block and an internal 1 V or 1.2 V analog

reference, which together support capacitive sensing of up to

33 inputs

[2]

. Capacitive sensing is configurable on each GPIO

pin. Scanning of enabled CapSense pins are completed quickly

and easily across multiple ports.

SmartSense?

SmartSense is an innovative solution from Cypress that removes

manual tuning of CapSense applications. This solution is easy to

use and provides a robust noise immunity. It is the only autotuning solution that establishes, monitors, and maintains all

required tuning parameters. SmartSense allows engineers to go

from prototyping to mass production without re-tuning for

manufacturing variations in PCB and/or overlay material

properties.

Figure 1. CapSense System Block Diagram

Analog Multiplexer System

The Analog Mux Bus can connect to every GPIO pin. Pins are

connected to the bus individually or in any combination. The bus

also connects to the analog system for analysis with the

CapSense block comparator.

Switch control logic enables selected pins to precharge

continuously under hardware control. This enables capacitive

measurement for applications such as touch sensing. Other

multiplexer applications include:

■ Complex capacitive sensing interfaces, such as sliders and

touchpads.

■ Chip-wide mux that allows analog input from any I/O pin.

■ Crosspoint connection between any I/O pin combinations.

The analog system contains the capacitive sensing hardware.

Several hardware algorithms are supported. This hardware

performs capacitive sensing and scanning without requiring

external components. The analog system is composed of the

CapSense PSoC block and an internal 1 V or 1.2 V analog

reference, which together support capacitive sensing of up to

33 inputs

[2]

. Capacitive sensing is configurable on each GPIO

pin. Scanning of enabled CapSense pins are completed quickly

and easily across multiple ports.

SmartSense?

SmartSense is an innovative solution from Cypress that removes

manual tuning of CapSense applications. This solution is easy to

use and provides a robust noise immunity. It is the only autotuning solution that establishes, monitors, and maintains all

required tuning parameters. SmartSense allows engineers to go

from prototyping to mass production without re-tuning for

manufacturing variations in PCB and/or overlay material

properties.

Figure 1. CapSense System Block Diagram

Analog Multiplexer System

The Analog Mux Bus can connect to every GPIO pin. Pins are

connected to the bus individually or in any combination. The bus

also connects to the analog system for analysis with the

CapSense block comparator.

Switch control logic enables selected pins to precharge

continuously under hardware control. This enables capacitive

measurement for applications such as touch sensing. Other

multiplexer applications include:

■ Complex capacitive sensing interfaces, such as sliders and

touchpads.

■ Chip-wide mux that allows analog input from any I/O pin.

■ Crosspoint connection between any I/O pin combinations.

CY8C20236A PSoC? Functional Overview

CY8C20236A PSoC? Functional Overview

The PSoC family consists of on-chip controller devices, which

are designed to replace multiple traditional microcontroller unit

(MCU)-based components with one, low cost single-chip

programmable component. A PSoC device includes

configurable analog and digital blocks, and programmable

interconnect. This architecture allows the user to create

customized peripheral configurations, to match the requirements

of each individual application. Additionally, a fast CPU, Flash

program memory, SRAM data memory, and configurable I/O are

included in a range of convenient pinouts.

The architecture for this device family, as shown in the Logic

Block Diagram on page 2, consists of three main areas:

■ The Core

■ CapSense Analog System

■ System Resources (including a full-speed USB port).

A common, versatile bus allows connection between I/O and the

analog system.

Each CY8C20x36A/66A PSoC device includes a dedicated

CapSense block that provides sensing and scanning control

circuitry for capacitive sensing applications. Depending on the

PSoC package, up to 36 GPIO are also included. The GPIO

provides access to the MCU and analog mux.

PSoC Core

The PSoC Core is a powerful engine that supports a rich

instruction set. It encompasses SRAM for data storage, an

interrupt controller, sleep and watchdog timers, and IMO and

ILO. The CPU core, called the M8C, is a powerful processor with

speeds up to 24 MHz. The M8C is a 4-MIPS,

8-bit Harvard-architecture microprocessor.

The PSoC family consists of on-chip controller devices, which

are designed to replace multiple traditional microcontroller unit

(MCU)-based components with one, low cost single-chip

programmable component. A PSoC device includes

configurable analog and digital blocks, and programmable

interconnect. This architecture allows the user to create

customized peripheral configurations, to match the requirements

of each individual application. Additionally, a fast CPU, Flash

program memory, SRAM data memory, and configurable I/O are

included in a range of convenient pinouts.

The architecture for this device family, as shown in the Logic

Block Diagram on page 2, consists of three main areas:

■ The Core

■ CapSense Analog System

■ System Resources (including a full-speed USB port).

A common, versatile bus allows connection between I/O and the

analog system.

Each CY8C20x36A/66A PSoC device includes a dedicated

CapSense block that provides sensing and scanning control

circuitry for capacitive sensing applications. Depending on the

PSoC package, up to 36 GPIO are also included. The GPIO

provides access to the MCU and analog mux.

PSoC Core

The PSoC Core is a powerful engine that supports a rich

instruction set. It encompasses SRAM for data storage, an

interrupt controller, sleep and watchdog timers, and IMO and

ILO. The CPU core, called the M8C, is a powerful processor with

speeds up to 24 MHz. The M8C is a 4-MIPS,

8-bit Harvard-architecture microprocessor.

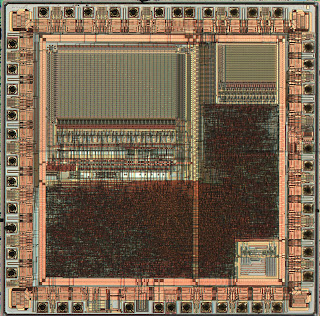

CY8C20236A MCU Code Reading

CY8C20236A MCU Code Reading, Code recover,chip reverse, chip programm reading, chip decryption.

Features

■ Automotive Electronics Council (AEC) Q100 qualified

■ Operating Range: 1.71 V to 5.5 V

■ Low power CapSense

?

block

? Configurable capacitive sensing elements

? Supports SmartSense

? Supports a combination of CapSense buttons, sliders,

touchpads, touchscreens, and proximity sensors

■ Powerful Harvard-architecture processor

? M8C CPU speed can be up to 24 MHz or sourced by an

external crystal, resonator, or clock signal

? Low power at high speed

? Interrupt controller

? Temperature range: –40 °C to +85 °C

■ Flexible on-chip memory

? Two program/data storage size options:

? CY8C20x36A: 8 KB flash/1 KB SRAM

? CY8C20x66A: 32 KB flash/2 KB SRAM

? 1,000 flash erase/write cycles

? Partial flash updates

? Flexible protection modes

? In-system serial programming (ISSP)

■ Precision, programmable clocking

? Internal main oscillator (IMO): 6/12/24 MHz ± 5%

? Internal low speed oscillator (ILO) at 32 kHz for watchdog

and sleep timers

? Precision 32 kHz oscillator for optional external crystal

■ Programmable pin configurations

? Up to 36 general-purpose I/Os (GPIOs) (depending on

package)

? Dual mode GPIO: All GPIOs support digital I/O and analog

inputs

? 25-mA sink current on each GPIO

? 120 mA total sink current on all GPIOs

? Pull-up, high Z, open-drain modes on all GPIOs

? CMOS drive mode – 5 mA source current on ports 0 and 1

and 1 mA on ports 2, 3, and 4

? 20 mA total source current on all GPIOs

? Selectable, regulated digital I/O on port 1

? Configurable input threshold on port 1

? Hot-swap capability on all Port 1 GPIO

■ Versatile analog mux

? Common internal analog bus

? Simultaneous connection of I/O

? High power supply rejection ratio (PSRR) comparator

? Low-dropout voltage regulator for all analog resources

■ Additional system resources

? I

2

C Slave:

? Selectable to 50 kHz, 100 kHz, or 400 kHz

? No clock stretching (under most conditions)

? Implementation during sleep modes with less than 100 μA

? Hardware address validation

? SPI master and slave: Configurable 46.9 kHz to 12 MHz

? Three 16-bit timers

? Watchdog and sleep timers

? Internal voltage reference

? Integrated supervisory circuit

? 8 to 10-bit incremental analog-to-digital converter (ADC)

? Two general-purpose high speed, low power analog

comparators

■ Complete development tools

? Free development tool (PSoC Designer?)

? Full-featured, in-circuit emulator (ICE) and programmer

? Full-speed emulation

? Complex breakpoint structure

? 128 KB trace memory

■ Package options

? CY8C20x36A:16-Pin 3 × 3 × 0.6 mm QFN

? CY8C20x66A: 48-Pin SSOP

Features

■ Automotive Electronics Council (AEC) Q100 qualified

■ Operating Range: 1.71 V to 5.5 V

■ Low power CapSense

?

block

? Configurable capacitive sensing elements

? Supports SmartSense

? Supports a combination of CapSense buttons, sliders,

touchpads, touchscreens, and proximity sensors

■ Powerful Harvard-architecture processor

? M8C CPU speed can be up to 24 MHz or sourced by an

external crystal, resonator, or clock signal

? Low power at high speed

? Interrupt controller

? Temperature range: –40 °C to +85 °C

■ Flexible on-chip memory

? Two program/data storage size options:

? CY8C20x36A: 8 KB flash/1 KB SRAM

? CY8C20x66A: 32 KB flash/2 KB SRAM

? 1,000 flash erase/write cycles

? Partial flash updates

? Flexible protection modes

? In-system serial programming (ISSP)

■ Precision, programmable clocking

? Internal main oscillator (IMO): 6/12/24 MHz ± 5%

? Internal low speed oscillator (ILO) at 32 kHz for watchdog

and sleep timers

? Precision 32 kHz oscillator for optional external crystal

■ Programmable pin configurations

? Up to 36 general-purpose I/Os (GPIOs) (depending on

package)

? Dual mode GPIO: All GPIOs support digital I/O and analog

inputs

? 25-mA sink current on each GPIO

? 120 mA total sink current on all GPIOs

? Pull-up, high Z, open-drain modes on all GPIOs

? CMOS drive mode – 5 mA source current on ports 0 and 1

and 1 mA on ports 2, 3, and 4

? 20 mA total source current on all GPIOs

? Selectable, regulated digital I/O on port 1

? Configurable input threshold on port 1

? Hot-swap capability on all Port 1 GPIO

■ Versatile analog mux

? Common internal analog bus

? Simultaneous connection of I/O

? High power supply rejection ratio (PSRR) comparator

? Low-dropout voltage regulator for all analog resources

■ Additional system resources

? I

2

C Slave:

? Selectable to 50 kHz, 100 kHz, or 400 kHz

? No clock stretching (under most conditions)

? Implementation during sleep modes with less than 100 μA

? Hardware address validation

? SPI master and slave: Configurable 46.9 kHz to 12 MHz

? Three 16-bit timers

? Watchdog and sleep timers

? Internal voltage reference

? Integrated supervisory circuit

? 8 to 10-bit incremental analog-to-digital converter (ADC)

? Two general-purpose high speed, low power analog

comparators

■ Complete development tools

? Free development tool (PSoC Designer?)

? Full-featured, in-circuit emulator (ICE) and programmer

? Full-speed emulation

? Complex breakpoint structure

? 128 KB trace memory

■ Package options

? CY8C20x36A:16-Pin 3 × 3 × 0.6 mm QFN

? CY8C20x66A: 48-Pin SSOP

2012年10月18日星期四

CY7C09099V-7AXI Code Extract

CY7C09099V-7AXI Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

Features

True Dual-Ported memory cells which enable simultaneous

access of the same memory location

Flow-through and Pipelined devices

32 K × 9 organizations (CY7C09179V)

64 K × 8 organizations (CY7C09089V)

128 K × 8/9 organizations (CY7C09099V/199V)

3 Modes

Flow-through

Pipelined

Burst

Pipelined output mode on both ports enables fast 100 MHz

operation

0.35-micron CMOS for optimum speed and power

High speed clock to data access 6.5

[1]

/7.5

[1]

/9/12 ns (max.)

3.3 V low operating power

Active = 115 mA (typical)

Standby = 10 ?A (typical)

Fully synchronous interface for easier operation

Burst counters increment addresses internally

Shorten cycle times

Minimize bus noise

Supported in Flow-through and Pipelined modes

Dual Chip Enables for easy depth expansion

Automatic power down

Commercial and Industrial temperature ranges

Available in 100-pin TQFP

Pb-free packages available

Features

True Dual-Ported memory cells which enable simultaneous

access of the same memory location

Flow-through and Pipelined devices

32 K × 9 organizations (CY7C09179V)

64 K × 8 organizations (CY7C09089V)

128 K × 8/9 organizations (CY7C09099V/199V)

3 Modes

Flow-through

Pipelined

Burst

Pipelined output mode on both ports enables fast 100 MHz

operation

0.35-micron CMOS for optimum speed and power

High speed clock to data access 6.5

[1]

/7.5

[1]

/9/12 ns (max.)

3.3 V low operating power

Active = 115 mA (typical)

Standby = 10 ?A (typical)

Fully synchronous interface for easier operation

Burst counters increment addresses internally

Shorten cycle times

Minimize bus noise

Supported in Flow-through and Pipelined modes

Dual Chip Enables for easy depth expansion

Automatic power down

Commercial and Industrial temperature ranges

Available in 100-pin TQFP

Pb-free packages available

CY7C0832BV-133AI Code Extract

CY7C0832BV-133AI Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

The FLEx18? family includes 2-Mbit, 4-Mbit, and 9-Mbit

pipelined, synchronous, true dual port static RAMs that are high

speed, low power 3.3 V CMOS. Two ports are provided,

permitting independent, simultaneous access to any location in

memory. The result of writing to the same location by more than

one port at the same time is undefined. Registers on control,

address, and data lines allow for minimal setup and hold time.

During a Read operation, data is registered for decreased cycle

time. Each port contains a burst counter on the input address

register. After externally loading the counter with the initial

address, the counter increments the address internally (more

details to follow). The internal Write pulse width is independent

of the duration of the R/W input signal. The internal Write pulse

is self-timed to allow the shortest possible cycle times.

A HIGH on CE0

or LOW on CE1

for one clock cycle powers down

the internal circuitry to reduce the static power consumption. One

cycle with chip enables asserted is required to reactivate the

outputs.

Additional features include: readback of burst-counter internal

address value on address lines, counter-mask registers to

control the counter wrap around, counter interrupt (CNTINT)

flags, readback of mask register value on address lines,

retransmit functionality, interrupt flags for message passing,

JTAG for boundary scan, and asynchronous Master Reset

(MRST).

The CY7C0833V device in this family has limited features. See

Address Counter and Mask Register Operations on page 7 for

details.

The FLEx18? family includes 2-Mbit, 4-Mbit, and 9-Mbit

pipelined, synchronous, true dual port static RAMs that are high

speed, low power 3.3 V CMOS. Two ports are provided,

permitting independent, simultaneous access to any location in

memory. The result of writing to the same location by more than

one port at the same time is undefined. Registers on control,

address, and data lines allow for minimal setup and hold time.

During a Read operation, data is registered for decreased cycle

time. Each port contains a burst counter on the input address

register. After externally loading the counter with the initial

address, the counter increments the address internally (more

details to follow). The internal Write pulse width is independent

of the duration of the R/W input signal. The internal Write pulse

is self-timed to allow the shortest possible cycle times.

A HIGH on CE0

or LOW on CE1

for one clock cycle powers down

the internal circuitry to reduce the static power consumption. One

cycle with chip enables asserted is required to reactivate the

outputs.

Additional features include: readback of burst-counter internal

address value on address lines, counter-mask registers to

control the counter wrap around, counter interrupt (CNTINT)

flags, readback of mask register value on address lines,

retransmit functionality, interrupt flags for message passing,

JTAG for boundary scan, and asynchronous Master Reset

(MRST).

The CY7C0833V device in this family has limited features. See

Address Counter and Mask Register Operations on page 7 for

details.

CY7C038V-20AXI Code Extract

CY7C038V-20AXI Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

Features

True dual-ported memory cells which allow

simultaneous access of the same memory location

32K x 16 organization (CY7C027V/027AV

[1]

)

64K x 16 organization (CY7C028V)

32K x 18 organization (CY7C037AV)

64K x 18 organization (CY7C038V)

0.35 micron Complementary metal oxide semiconductor

(CMOS) for optimum speed and power

High speed access: 15, 20, and 25 ns

Low operating power

Active: ICC = 115 mA (typical)

Standby: ISB3

= 10 ?A (typical)

Fully asynchronous operation

Automatic power-down

Expandable data bus to 32/36 bits or more using Master/Slave

chip select when using more than one device

On-chip arbitration logic

Semaphores included to permit software handshaking

between ports

INT flag for port-to-port communication

Separate upper-byte and lower-byte control

Dual chip enables

Pin select for Master or Slave

Commercial and Industrial temperature ranges

100-pin Pb-free Thin quad plastic flatpack (TQFP) and 100-pin

TQFP

Features

True dual-ported memory cells which allow

simultaneous access of the same memory location

32K x 16 organization (CY7C027V/027AV

[1]

)

64K x 16 organization (CY7C028V)

32K x 18 organization (CY7C037AV)

64K x 18 organization (CY7C038V)

0.35 micron Complementary metal oxide semiconductor

(CMOS) for optimum speed and power

High speed access: 15, 20, and 25 ns

Low operating power

Active: ICC = 115 mA (typical)

Standby: ISB3

= 10 ?A (typical)

Fully asynchronous operation

Automatic power-down

Expandable data bus to 32/36 bits or more using Master/Slave

chip select when using more than one device

On-chip arbitration logic

Semaphores included to permit software handshaking

between ports

INT flag for port-to-port communication

Separate upper-byte and lower-byte control

Dual chip enables

Pin select for Master or Slave

Commercial and Industrial temperature ranges

100-pin Pb-free Thin quad plastic flatpack (TQFP) and 100-pin

TQFP

CY7C0430CV-133BGI Code Extract

CY7C0430CV-133BGI Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

The Quadport Datapath Switching Element (DSE) family offers

four ports that may be clocked at independent frequencies

from one another. Each port can read or write up to 133 MHz

[]

,

giving the device up to 10 Gb/s of data throughput. The device

is 1-Mb (64K × 18) in density. Simultaneous reads are allowed

for accesses to the same address location; however, simultaneous reading and writing to the same address is not allowed.

Any port can write to a certain location while other ports are

reading that location simultaneously, if the timing spec for port

to port delay (tCCS) is met. The result of writing to the same

location by more than one port at the same time is undefined.

Data is registered for decreased cycle time. Clock to data valid

tCD2

= 4.2 ns. Each port contains a burst counter on the input

address register. After externally loading the counter with the

initial address the counter will self-increment the address internally (more details to follow). The internal write pulse width is

independent of the duration of the R/W input signal. The

internal write pulse is self-timed to allow the shortest possible

cycle times.

A HIGH on CE0

or LOW on CE1

for one clock cycle will power

down the internal circuitry to reduce the static power

consumption. One cycle is required with chip enables asserted

to reactivate the outputs.

The CY7C0430CV (64K × 18 device) supports burst contains

for simple array partitioning. Counter enable inputs are

provided to stall the operation of the address input and utilize

the internal address generated by the internal counter for fast

interleaved memory applications. A port’s burst counter is

loaded with an external address when the port’s Counter Load

pin (CNTLD) is asserted LOW. When the port’s Counter

Increment pin (CNTINC) is asserted, the address counter will

increment on each subsequent LOW-to- HIGH transition of

that port’s clock signal. This will read/write one word from/into

each successive address location until CNTINC is deasserted.

The counter can address the entire switch array and will loop

back to the start. Counter Reset (CNTRST) is used to reset the

burst counter. A counter-mask register is used to control the

counter wrap. The counter and mask register operations are

described in more details in the following sections.

The counter or mask register values can be read back on the

bidirectional address lines by activating MKRD or CNTRD,

respectively.

The new features included for the QuadPort DSE family

include: readback of burst-counter internal address value on

address lines, counter-mask registers to control the counter

wrap-around, readback of mask register value on address

lines, interrupt flags for message passing, BIST, JTAG for

boundary scan, and asynchronous Master Reset.

The Quadport Datapath Switching Element (DSE) family offers

four ports that may be clocked at independent frequencies

from one another. Each port can read or write up to 133 MHz

[]

,

giving the device up to 10 Gb/s of data throughput. The device

is 1-Mb (64K × 18) in density. Simultaneous reads are allowed

for accesses to the same address location; however, simultaneous reading and writing to the same address is not allowed.

Any port can write to a certain location while other ports are

reading that location simultaneously, if the timing spec for port

to port delay (tCCS) is met. The result of writing to the same

location by more than one port at the same time is undefined.

Data is registered for decreased cycle time. Clock to data valid

tCD2

= 4.2 ns. Each port contains a burst counter on the input

address register. After externally loading the counter with the

initial address the counter will self-increment the address internally (more details to follow). The internal write pulse width is

independent of the duration of the R/W input signal. The

internal write pulse is self-timed to allow the shortest possible

cycle times.

A HIGH on CE0

or LOW on CE1

for one clock cycle will power

down the internal circuitry to reduce the static power

consumption. One cycle is required with chip enables asserted

to reactivate the outputs.

The CY7C0430CV (64K × 18 device) supports burst contains

for simple array partitioning. Counter enable inputs are

provided to stall the operation of the address input and utilize

the internal address generated by the internal counter for fast

interleaved memory applications. A port’s burst counter is

loaded with an external address when the port’s Counter Load

pin (CNTLD) is asserted LOW. When the port’s Counter

Increment pin (CNTINC) is asserted, the address counter will

increment on each subsequent LOW-to- HIGH transition of

that port’s clock signal. This will read/write one word from/into

each successive address location until CNTINC is deasserted.

The counter can address the entire switch array and will loop

back to the start. Counter Reset (CNTRST) is used to reset the

burst counter. A counter-mask register is used to control the

counter wrap. The counter and mask register operations are

described in more details in the following sections.

The counter or mask register values can be read back on the

bidirectional address lines by activating MKRD or CNTRD,

respectively.

The new features included for the QuadPort DSE family

include: readback of burst-counter internal address value on

address lines, counter-mask registers to control the counter

wrap-around, readback of mask register value on address

lines, interrupt flags for message passing, BIST, JTAG for

boundary scan, and asynchronous Master Reset.

CY7C057V-12AXC Code Extract

CY7C057V-12AXC Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

Features

True dual-ported memory cells that allow simultaneous

access of the same memory location

16K x 36 organization (CY7C056V)

32K x 36 organization (CY7C057V)

0.25-micron Complimentary metal oxide semiconductor

(CMOS) for optimum speed/power

High-speed access: 12/15 ns

Low operating power

Active: ICC = 250 mA (typical)

Standby: ISB3

= 10 ?A (typical)

Fully asynchronous operation

Automatic power-down

Expandable data bus to 72 bits or more using Master/Slave

Chip Select when using more than one device

On-chip arbitration logic

Semaphores included to permit software handshaking

between ports

INT flag for port-to-port communication

Byte select on left port

Bus matching on right port

Depth expansion via dual chip enables

Pin select for Master or Slave

Commercial and Industrial temperature ranges

Available in 144-Pin Thin quad plastic flatpack (TQFP) or

172-Ball ball grid array (BGA)

Pb-free packages available

Compact packages:

144-Pin TQFP (20 x 20 x 1.4 mm)

172-Ball BGA (1.0-mm pitch) (15 x 15 x.51 mm)

Features

True dual-ported memory cells that allow simultaneous

access of the same memory location

16K x 36 organization (CY7C056V)

32K x 36 organization (CY7C057V)

0.25-micron Complimentary metal oxide semiconductor

(CMOS) for optimum speed/power

High-speed access: 12/15 ns

Low operating power

Active: ICC = 250 mA (typical)

Standby: ISB3

= 10 ?A (typical)

Fully asynchronous operation

Automatic power-down

Expandable data bus to 72 bits or more using Master/Slave

Chip Select when using more than one device

On-chip arbitration logic

Semaphores included to permit software handshaking

between ports

INT flag for port-to-port communication

Byte select on left port

Bus matching on right port

Depth expansion via dual chip enables

Pin select for Master or Slave

Commercial and Industrial temperature ranges

Available in 144-Pin Thin quad plastic flatpack (TQFP) or

172-Ball ball grid array (BGA)

Pb-free packages available

Compact packages:

144-Pin TQFP (20 x 20 x 1.4 mm)

172-Ball BGA (1.0-mm pitch) (15 x 15 x.51 mm)

CY7C0831AV-133AXI Code Extract

CY7C0831AV-133AXI Code Extract, cypress MCU decryption, cypress chip crack, cypress PCB clone .

Features

True dual-ported memory cells that allow simultaneous access

of the same memory location

Synchronous pipelined operation

Family of 2-Mbit, 4-Mbit, and 9-Mbit devices

Pipelined output mode allows fast operation

0.18 micron CMOS for optimum speed and power

High speed clock to data access

3.3 V low power

Active as low as 225 mA (typ)

Standby as low as 55 mA (typ)

Mailbox function for message passing

Global master reset

Separate byte enables on both ports

Commercial and Industrial temperature ranges

IEEE 1149.1 compatible JTAG boundary scan

144-ball FBGA (13 mm × 13 mm) (1.0 mm pitch)

120-pin TQFP (14 mm × 14 mm × 1.4 mm)

Pb-free packages available

Counter wrap around control

Internal mask register controls counter wrap around

Counter-interrupt flags to indicate wrap around

Memory block retransmit operation

Counter readback on address lines

Mask register readback on address lines

Dual chip enables on both ports for easy depth expansion

Features

True dual-ported memory cells that allow simultaneous access

of the same memory location

Synchronous pipelined operation

Family of 2-Mbit, 4-Mbit, and 9-Mbit devices

Pipelined output mode allows fast operation

0.18 micron CMOS for optimum speed and power

High speed clock to data access

3.3 V low power

Active as low as 225 mA (typ)

Standby as low as 55 mA (typ)

Mailbox function for message passing

Global master reset

Separate byte enables on both ports

Commercial and Industrial temperature ranges

IEEE 1149.1 compatible JTAG boundary scan

144-ball FBGA (13 mm × 13 mm) (1.0 mm pitch)

120-pin TQFP (14 mm × 14 mm × 1.4 mm)

Pb-free packages available

Counter wrap around control

Internal mask register controls counter wrap around

Counter-interrupt flags to indicate wrap around

Memory block retransmit operation

Counter readback on address lines

Mask register readback on address lines

Dual chip enables on both ports for easy depth expansion

2012年10月10日星期三

M32C/84 code extraction

M32C/84 Renesas series chip decryption, code extraction,

programm reading.

The M32C/84 is based on the M32C/80 CPU Core and has 16MB of

address space.Maximum operating frequency is 32MHz. Mask ROM,

Flash Memory, and ROM-lessVersions are available. Internal Flash

Memory is programmable on a single powersource.

Key Features:

16-bit Multifunction Timer (Timer A and B, incl. 3-phase

inverter motorcontrol function): 11 channels

Clock Synchronous / Asynchronous Serial Interface: 5 channels

10-bit A/D Converter: 34 channels*

8-bit D/A Converter: 2

DMAC: 4 channels

DMAC II: Can be activated by all peripheral function interrupt

factors

Intelligent I/O

Time Measurement (Input Capture) or Waveform Generating (Output

Compare)Function: 16-bit x 8 channels

Communication Function

2-phase Pulse Signal Processing (2-phase encoder input)

CAN: 1 channel (2.0B)

CRC Calculation Circuit

X/Y Converter

Watchdog Timer

Clock Generation Circuits: Main Clock Generation Circuit, Sub

ClockGeneration Circuit, On-chip Oscillator, PLL Synthesizer

Oscillation Stop Detection Function

Power Supply Voltage Detection (Except for T Version)

ROM Correction Function

I/O Ports: 123*

External Interrupt Pins: 11

Data Flash: 4KB (Flash Memory Version only)

*: Spec of 144-pin version.

Key Applications:

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

M30843MWT-XXXGP M30843MWU-XXXGP M30845FHUGP M30845FJTGP

M30845FJUGP M30845MGT-XXXGP M30845MGU-XXXGP M30845MHT-XXXGP

M30845MHU-XXXGP M30845MWT-XXXGP M30845MWU-XXXGP

programm reading.

The M32C/84 is based on the M32C/80 CPU Core and has 16MB of

address space.Maximum operating frequency is 32MHz. Mask ROM,

Flash Memory, and ROM-lessVersions are available. Internal Flash

Memory is programmable on a single powersource.

Key Features:

16-bit Multifunction Timer (Timer A and B, incl. 3-phase

inverter motorcontrol function): 11 channels

Clock Synchronous / Asynchronous Serial Interface: 5 channels

10-bit A/D Converter: 34 channels*

8-bit D/A Converter: 2

DMAC: 4 channels

DMAC II: Can be activated by all peripheral function interrupt

factors

Intelligent I/O

Time Measurement (Input Capture) or Waveform Generating (Output

Compare)Function: 16-bit x 8 channels

Communication Function

2-phase Pulse Signal Processing (2-phase encoder input)

CAN: 1 channel (2.0B)

CRC Calculation Circuit

X/Y Converter

Watchdog Timer

Clock Generation Circuits: Main Clock Generation Circuit, Sub

ClockGeneration Circuit, On-chip Oscillator, PLL Synthesizer

Oscillation Stop Detection Function

Power Supply Voltage Detection (Except for T Version)

ROM Correction Function

I/O Ports: 123*

External Interrupt Pins: 11

Data Flash: 4KB (Flash Memory Version only)

*: Spec of 144-pin version.

Key Applications:

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

M30843MWT-XXXGP M30843MWU-XXXGP M30845FHUGP M30845FJTGP

M30845FJUGP M30845MGT-XXXGP M30845MGU-XXXGP M30845MHT-XXXGP

M30845MHU-XXXGP M30845MWT-XXXGP M30845MWU-XXXGP

M30843FHFP Key Applications

Key Applications:

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

M30843MWT-XXXGP M30843MWU-XXXGP M30845FHUGP M30845FJTGP

M30845FJUGP M30845MGT-XXXGP M30845MGU-XXXGP M30845MHT-XXXGP

M30845MHU-XXXGP M30845MWT-XXXGP M30845MWU-XXXGP

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

M30843MWT-XXXGP M30843MWU-XXXGP M30845FHUGP M30845FJTGP

M30845FJUGP M30845MGT-XXXGP M30845MGU-XXXGP M30845MHT-XXXGP

M30845MHU-XXXGP M30845MWT-XXXGP M30845MWU-XXXGP

M30840MC-XXXFP Key Applications

Key Applications:

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

Automobiles, Audio, Cameras, Office Equipment,

Communication/PortableDevices.

M30840MC-XXXFP M30840MC-XXXGP M30840SFP M30840SGP M30842MC-XXXGP

M30842SGP M30843FHFP M30843FHGP M30843FJFP M30843FJGP M30843FWGP

M30843MW-XXXFP M30843MW-XXXGP M30845FHGP M30845FJGP M30845FWGP

M30845MW-XXXGP M30840MCT-XXXGP M30842MCT-XXXGP M30843FJTGP

M30843MGT-XXXGP M30843MGU-XXXGP M30843MHT-XXXGP M30843MHU-XXXGP

M32C/84 Key Features

16-bit Multifunction Timer (Timer A and B, incl. 3-phase

inverter motorcontrol function): 11 channels

Clock Synchronous / Asynchronous Serial Interface: 5 channels

10-bit A/D Converter: 34 channels*

8-bit D/A Converter: 2

DMAC: 4 channels

DMAC II: Can be activated by all peripheral function interrupt

factors

Intelligent I/O

Time Measurement (Input Capture) or Waveform Generating (Output

Compare)Function: 16-bit x 8 channels

Communication Function

2-phase Pulse Signal Processing (2-phase encoder input)

CAN: 1 channel (2.0B)

CRC Calculation Circuit

X/Y Converter

Watchdog Timer

Clock Generation Circuits: Main Clock Generation Circuit, Sub

ClockGeneration Circuit, On-chip Oscillator, PLL Synthesizer

Oscillation Stop Detection Function

Power Supply Voltage Detection (Except for T Version)

ROM Correction Function

I/O Ports: 123*

External Interrupt Pins: 11

Data Flash: 4KB (Flash Memory Version only)

*: Spec of 144-pin version.

inverter motorcontrol function): 11 channels

Clock Synchronous / Asynchronous Serial Interface: 5 channels

10-bit A/D Converter: 34 channels*

8-bit D/A Converter: 2

DMAC: 4 channels

DMAC II: Can be activated by all peripheral function interrupt

factors

Intelligent I/O

Time Measurement (Input Capture) or Waveform Generating (Output

Compare)Function: 16-bit x 8 channels

Communication Function

2-phase Pulse Signal Processing (2-phase encoder input)

CAN: 1 channel (2.0B)

CRC Calculation Circuit

X/Y Converter

Watchdog Timer

Clock Generation Circuits: Main Clock Generation Circuit, Sub

ClockGeneration Circuit, On-chip Oscillator, PLL Synthesizer

Oscillation Stop Detection Function

Power Supply Voltage Detection (Except for T Version)

ROM Correction Function

I/O Ports: 123*

External Interrupt Pins: 11

Data Flash: 4KB (Flash Memory Version only)

*: Spec of 144-pin version.

M32C/84 Renesas series chip decryption

M32C/84 Renesas series chip decryption, code extraction,

programm reading.

The M32C/84 is based on the M32C/80 CPU Core and has 16MB of

address space.Maximum operating frequency is 32MHz. Mask ROM,

Flash Memory, and ROM-lessVersions are available. Internal Flash

Memory is programmable on a single powersource.

programm reading.

The M32C/84 is based on the M32C/80 CPU Core and has 16MB of

address space.Maximum operating frequency is 32MHz. Mask ROM,

Flash Memory, and ROM-lessVersions are available. Internal Flash

Memory is programmable on a single powersource.

2012年9月25日星期二

PIC18F14K50 MCU CRACK

PIC18F14K50 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

The PIC18F14K50 brings advanced features and exceptional value

to the embedded USB market. This low cost PIC® Microcontroller

features a full speed USB 2.0 compliant interface that can

automatically change clock sources and power levels upon

connection to a host, making it an exceptional device for

battery-powered applications. The addition of mTouch(TM) touch

sensing compatibility, a 10-bit ADC, motor control PWMs, and a

host of serial interfaces make the PIC18F14K50 the perfect

device to "Just add USB" to any application.

USB Application Design Center Debug Support

• A debug header is required for this device

• Part Numbers:, AC244023 (F) / AC244024 (LF)

• Debug and programming support is available via MPLAB® REAL

ICE, PICkit™ 3, and MPLAB® ICD 3

• For Debug Header information, please refer to DS51292

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

The PIC18F14K50 brings advanced features and exceptional value

to the embedded USB market. This low cost PIC® Microcontroller

features a full speed USB 2.0 compliant interface that can

automatically change clock sources and power levels upon

connection to a host, making it an exceptional device for

battery-powered applications. The addition of mTouch(TM) touch

sensing compatibility, a 10-bit ADC, motor control PWMs, and a

host of serial interfaces make the PIC18F14K50 the perfect

device to "Just add USB" to any application.

USB Application Design Center Debug Support

• A debug header is required for this device

• Part Numbers:, AC244023 (F) / AC244024 (LF)

• Debug and programming support is available via MPLAB® REAL

ICE, PICkit™ 3, and MPLAB® ICD 3

• For Debug Header information, please refer to DS51292

PIC18F24K22 MCU CRACK

PIC18F24K22 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler optimized architecture/instruction set

Data EEPROM to 1024 bytes

Linear program memory addressing to 64 Kbytes

Linear data memory addressing to 4 Kbytes

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 Single-Cycle Hardware MultiplierExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA, typical

Watchdog Timer: 500 nA, typical

Timer1 Oscillator: 500 nA @ typical 32 kHzFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four Crystal modes up to 64 MHz

Two external Clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops

Two-Speed Oscillator Start-upSpecial Microcontroller Features:

Full 5.5V operation (PIC18F2XK22/4XK22)

Low voltage option available for 1.8V-3.6V operation

(PIC18LF2XK22/4XK22)

Self-reprogrammable under software control

Power-on Reset (POR), Power-up Timer (PWRT)and Oscillator Start

-up Timer (OST)

Programmable Brown-out Reset (BOR)

Extended Watchdog Timer (WDT) with on-chiposcillator and

software enable

Programmable code protection

In-Circuit Serial Programming™ (ICSP™) viatwo pins

In-Circuit Debug via two pinsAnalog Features:

Analog-to-Digital Converter (ADC) module:- 10-bit resolution- 17

analog input channels (PIC18F/LF2XK22)- 28 analog input channels

(PIC18F/LF4XK22)- Auto acquisition capability- Conversion

available during Sleep

Programmable High/Low Voltage Detection(PLVD) module

Charge Time Measurement Unit (CTMU) formTouch™ support:- Up to

28 channels for button, sensor or sliderinput

Analog comparator module with:- Two rail-to-rail analog

comparators- Comparator inputs and outputs externallyaccessible

and configurable

Voltage reference module with:- Programmable On-chip Voltage

Reference(CVREF) module (% of VDD)- Selectable on-chip fixed

voltage referencePeripheral Features:

24/35 I/O pins and 1 input-only pin:- High current sink/source

25 mA/25 mA- Individually programmable weak pull-ups-

Individually programmable interrupt-on-pinchange

Three external interrupt pins

Up to seven Timer modules:- Up to four 16-bit timers/counters

with prescaler- Up to three 8-bit timers/counters- Dedicated,

low-power Timer1 oscillator

Up to two Capture/Compare/PWM (CCP) modules

Up to three Enhanced Capture/Compare/PWM(ECCP) modules with:-

One, two or four PWM outputs- Selectable polarity- Programmable

dead time- Auto-shutdown and Auto-restart- PWM output steering

control

Two Master Synchronous Serial Port (MSSP)modules with two modes

of operation:- 3-wire SPI (supports all 4 SPI modes)- I2C™

Master and Slave modes (Slave modewith address masking)

Two Enhanced Universal Synchronous AsynchronousReceiver

Transmitter modules (EUSART):- Supports RS-232, RS-485 and LIN

2.0- Auto-Baud Detect- Auto Wake-up on Start bit

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler optimized architecture/instruction set

Data EEPROM to 1024 bytes

Linear program memory addressing to 64 Kbytes

Linear data memory addressing to 4 Kbytes

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 Single-Cycle Hardware MultiplierExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA, typical

Watchdog Timer: 500 nA, typical

Timer1 Oscillator: 500 nA @ typical 32 kHzFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four Crystal modes up to 64 MHz

Two external Clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops

Two-Speed Oscillator Start-upSpecial Microcontroller Features:

Full 5.5V operation (PIC18F2XK22/4XK22)

Low voltage option available for 1.8V-3.6V operation

(PIC18LF2XK22/4XK22)

Self-reprogrammable under software control

Power-on Reset (POR), Power-up Timer (PWRT)and Oscillator Start

-up Timer (OST)

Programmable Brown-out Reset (BOR)

Extended Watchdog Timer (WDT) with on-chiposcillator and

software enable

Programmable code protection

In-Circuit Serial Programming™ (ICSP™) viatwo pins

In-Circuit Debug via two pinsAnalog Features:

Analog-to-Digital Converter (ADC) module:- 10-bit resolution- 17

analog input channels (PIC18F/LF2XK22)- 28 analog input channels

(PIC18F/LF4XK22)- Auto acquisition capability- Conversion

available during Sleep

Programmable High/Low Voltage Detection(PLVD) module

Charge Time Measurement Unit (CTMU) formTouch™ support:- Up to

28 channels for button, sensor or sliderinput

Analog comparator module with:- Two rail-to-rail analog

comparators- Comparator inputs and outputs externallyaccessible

and configurable

Voltage reference module with:- Programmable On-chip Voltage

Reference(CVREF) module (% of VDD)- Selectable on-chip fixed

voltage referencePeripheral Features:

24/35 I/O pins and 1 input-only pin:- High current sink/source

25 mA/25 mA- Individually programmable weak pull-ups-

Individually programmable interrupt-on-pinchange

Three external interrupt pins

Up to seven Timer modules:- Up to four 16-bit timers/counters

with prescaler- Up to three 8-bit timers/counters- Dedicated,

low-power Timer1 oscillator

Up to two Capture/Compare/PWM (CCP) modules

Up to three Enhanced Capture/Compare/PWM(ECCP) modules with:-

One, two or four PWM outputs- Selectable polarity- Programmable

dead time- Auto-shutdown and Auto-restart- PWM output steering

control

Two Master Synchronous Serial Port (MSSP)modules with two modes

of operation:- 3-wire SPI (supports all 4 SPI modes)- I2C™

Master and Slave modes (Slave modewith address masking)

Two Enhanced Universal Synchronous AsynchronousReceiver

Transmitter modules (EUSART):- Supports RS-232, RS-485 and LIN

2.0- Auto-Baud Detect- Auto Wake-up on Start bit

PIC18F43K20 MCU CRACK

PIC18F43K20 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler Optimized Architecture:- Optional extended

instruction set designed tooptimize re-entrant code

Up to 1024 bytes Data EEPROM

Up to 64 Kbytes Linear program memoryaddressing

Up to 3936 bytes Linear data memory addressing

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 single-cycle hardware multiplierFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four crystal modes up to 64 MHz

Two external clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops- Two-Speed Oscillator Start-upSpecial Microcontroller

Features:

Operating Voltage Range: 1.8V to 3.6V

Self-Programmable under Software Control

Programmable 16-Level High/Low-VoltageDetection (HLVD) module:-

Interrupt on High/Low-Voltage Detection

Programmable Brown-out Reset (BOR):- With software enable option

Extended Watchdog Timer (WDT):- Programmable period from 4 ms to

131s

Single-Supply 3V In-Circuit SerialProgramming™ (ICSP™) via two

pins

In-Circuit Debug (ICD) via Two PinsExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA

Watchdog Timer: 500 nA

Timer1 Oscillator: 500 nA @ 32 kHzAnalog Features:

Analog-to-Digital Converter (ADC) module :- 10-bit resolution,

13 External Channels- Auto-acquisition capability- Conversion

available during Sleep- 1.2V Fixed Voltage Reference (FVR)

channel- Independent input multiplexing

Analog Comparator module:- Two rail-to-rail analog comparators-

Independent input multiplexing

Voltage Reference (CVREF) module- Programmable (% VDD), 16

steps- Two 16-level voltage ranges using VREF pinsPeripheral

Highlights:

Up to 35 I/O pins plus 1 input-only pin:- High-Current

Sink/Source 25 mA/25 mA- Three programmable external interrupts-

Four programmable interrupt-on-change- Eight programmable weak

pull-ups- Programmable slew rate

Capture/Compare/PWM (CCP) module

Enhanced CCP (ECCP) module:- One, two or four PWM outputs-

Selectable polarity- Programmable dead time- Auto-Shutdown and

Auto-Restart

Master Synchronous Serial Port (MSSP) module- 3-wire SPI

(supports all 4 modes)- I2C™ Master and Slave modes with

addressmask

Enhanced Universal Synchronous AsynchronousReceiver Transmitter

(EUSART) module:- Supports RS-485, RS-232 and LIN- RS-232

operation using internal oscillator- Auto-Wake-up on Break-

Auto-Baud Detect

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler Optimized Architecture:- Optional extended

instruction set designed tooptimize re-entrant code

Up to 1024 bytes Data EEPROM

Up to 64 Kbytes Linear program memoryaddressing

Up to 3936 bytes Linear data memory addressing

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 single-cycle hardware multiplierFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four crystal modes up to 64 MHz

Two external clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops- Two-Speed Oscillator Start-upSpecial Microcontroller

Features:

Operating Voltage Range: 1.8V to 3.6V

Self-Programmable under Software Control

Programmable 16-Level High/Low-VoltageDetection (HLVD) module:-

Interrupt on High/Low-Voltage Detection

Programmable Brown-out Reset (BOR):- With software enable option

Extended Watchdog Timer (WDT):- Programmable period from 4 ms to

131s

Single-Supply 3V In-Circuit SerialProgramming™ (ICSP™) via two

pins

In-Circuit Debug (ICD) via Two PinsExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA

Watchdog Timer: 500 nA

Timer1 Oscillator: 500 nA @ 32 kHzAnalog Features:

Analog-to-Digital Converter (ADC) module :- 10-bit resolution,

13 External Channels- Auto-acquisition capability- Conversion

available during Sleep- 1.2V Fixed Voltage Reference (FVR)

channel- Independent input multiplexing

Analog Comparator module:- Two rail-to-rail analog comparators-

Independent input multiplexing

Voltage Reference (CVREF) module- Programmable (% VDD), 16

steps- Two 16-level voltage ranges using VREF pinsPeripheral

Highlights:

Up to 35 I/O pins plus 1 input-only pin:- High-Current

Sink/Source 25 mA/25 mA- Three programmable external interrupts-

Four programmable interrupt-on-change- Eight programmable weak

pull-ups- Programmable slew rate

Capture/Compare/PWM (CCP) module

Enhanced CCP (ECCP) module:- One, two or four PWM outputs-

Selectable polarity- Programmable dead time- Auto-Shutdown and

Auto-Restart

Master Synchronous Serial Port (MSSP) module- 3-wire SPI

(supports all 4 modes)- I2C™ Master and Slave modes with

addressmask

Enhanced Universal Synchronous AsynchronousReceiver Transmitter

(EUSART) module:- Supports RS-485, RS-232 and LIN- RS-232

operation using internal oscillator- Auto-Wake-up on Break-

Auto-Baud Detect

PIC18F25K20 MCU CRACK

PIC18F25K20 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler Optimized Architecture:- Optional extended

instruction set designed tooptimize re-entrant code

Up to 1024 bytes Data EEPROM

Up to 64 Kbytes Linear program memoryaddressing

Up to 3936 bytes Linear data memory addressing

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 single-cycle hardware multiplierFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four crystal modes up to 64 MHz

Two external clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops- Two-Speed Oscillator Start-upSpecial Microcontroller

Features:

Operating Voltage Range: 1.8V to 3.6V

Self-Programmable under Software Control

Programmable 16-Level High/Low-VoltageDetection (HLVD) module:-

Interrupt on High/Low-Voltage Detection

Programmable Brown-out Reset (BOR):- With software enable option

Extended Watchdog Timer (WDT):- Programmable period from 4 ms to

131s

Single-Supply 3V In-Circuit SerialProgramming™ (ICSP™) via two

pins

In-Circuit Debug (ICD) via Two PinsExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA

Watchdog Timer: 500 nA

Timer1 Oscillator: 500 nA @ 32 kHzAnalog Features:

Analog-to-Digital Converter (ADC) module :- 10-bit resolution,

13 External Channels- Auto-acquisition capability- Conversion

available during Sleep- 1.2V Fixed Voltage Reference (FVR)

channel- Independent input multiplexing

Analog Comparator module:- Two rail-to-rail analog comparators-

Independent input multiplexing

Voltage Reference (CVREF) module- Programmable (% VDD), 16

steps- Two 16-level voltage ranges using VREF pinsPeripheral

Highlights:

Up to 35 I/O pins plus 1 input-only pin:- High-Current

Sink/Source 25 mA/25 mA- Three programmable external interrupts-

Four programmable interrupt-on-change- Eight programmable weak

pull-ups- Programmable slew rate

Capture/Compare/PWM (CCP) module

Enhanced CCP (ECCP) module:- One, two or four PWM outputs-

Selectable polarity- Programmable dead time- Auto-Shutdown and

Auto-Restart

Master Synchronous Serial Port (MSSP) module- 3-wire SPI

(supports all 4 modes)- I2C™ Master and Slave modes with

addressmask

Enhanced Universal Synchronous AsynchronousReceiver Transmitter

(EUSART) module:- Supports RS-485, RS-232 and LIN- RS-232

operation using internal oscillator- Auto-Wake-up on Break-

Auto-Baud Detect

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler Optimized Architecture:- Optional extended

instruction set designed tooptimize re-entrant code

Up to 1024 bytes Data EEPROM

Up to 64 Kbytes Linear program memoryaddressing

Up to 3936 bytes Linear data memory addressing

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 single-cycle hardware multiplierFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four crystal modes up to 64 MHz

Two external clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops- Two-Speed Oscillator Start-upSpecial Microcontroller

Features:

Operating Voltage Range: 1.8V to 3.6V

Self-Programmable under Software Control

Programmable 16-Level High/Low-VoltageDetection (HLVD) module:-

Interrupt on High/Low-Voltage Detection

Programmable Brown-out Reset (BOR):- With software enable option

Extended Watchdog Timer (WDT):- Programmable period from 4 ms to

131s

Single-Supply 3V In-Circuit SerialProgramming™ (ICSP™) via two

pins

In-Circuit Debug (ICD) via Two PinsExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA

Watchdog Timer: 500 nA

Timer1 Oscillator: 500 nA @ 32 kHzAnalog Features:

Analog-to-Digital Converter (ADC) module :- 10-bit resolution,

13 External Channels- Auto-acquisition capability- Conversion

available during Sleep- 1.2V Fixed Voltage Reference (FVR)

channel- Independent input multiplexing

Analog Comparator module:- Two rail-to-rail analog comparators-

Independent input multiplexing

Voltage Reference (CVREF) module- Programmable (% VDD), 16

steps- Two 16-level voltage ranges using VREF pinsPeripheral

Highlights:

Up to 35 I/O pins plus 1 input-only pin:- High-Current

Sink/Source 25 mA/25 mA- Three programmable external interrupts-

Four programmable interrupt-on-change- Eight programmable weak

pull-ups- Programmable slew rate

Capture/Compare/PWM (CCP) module

Enhanced CCP (ECCP) module:- One, two or four PWM outputs-

Selectable polarity- Programmable dead time- Auto-Shutdown and

Auto-Restart

Master Synchronous Serial Port (MSSP) module- 3-wire SPI

(supports all 4 modes)- I2C™ Master and Slave modes with

addressmask

Enhanced Universal Synchronous AsynchronousReceiver Transmitter

(EUSART) module:- Supports RS-485, RS-232 and LIN- RS-232

operation using internal oscillator- Auto-Wake-up on Break-

Auto-Baud Detect

PIC18F23K22 MCU CRACK

PIC18F23K22 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler optimized architecture/instruction set

Data EEPROM to 1024 bytes

Linear program memory addressing to 64 Kbytes

Linear data memory addressing to 4 Kbytes

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 Single-Cycle Hardware MultiplierExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA, typical

Watchdog Timer: 500 nA, typical

Timer1 Oscillator: 500 nA @ typical 32 kHzFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four Crystal modes up to 64 MHz

Two external Clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops

Two-Speed Oscillator Start-upSpecial Microcontroller Features:

Full 5.5V operation (PIC18F2XK22/4XK22)

Low voltage option available for 1.8V-3.6V operation

(PIC18LF2XK22/4XK22)

Self-reprogrammable under software control

Power-on Reset (POR), Power-up Timer (PWRT)and Oscillator Start

-up Timer (OST)

Programmable Brown-out Reset (BOR)

Extended Watchdog Timer (WDT) with on-chiposcillator and

software enable

Programmable code protection

In-Circuit Serial Programming™ (ICSP™) viatwo pins

In-Circuit Debug via two pinsAnalog Features:

Analog-to-Digital Converter (ADC) module:- 10-bit resolution- 17

analog input channels (PIC18F/LF2XK22)- 28 analog input channels

(PIC18F/LF4XK22)- Auto acquisition capability- Conversion

available during Sleep

Programmable High/Low Voltage Detection(PLVD) module

Charge Time Measurement Unit (CTMU) formTouch™ support:- Up to

28 channels for button, sensor or sliderinput

Analog comparator module with:- Two rail-to-rail analog

comparators- Comparator inputs and outputs externallyaccessible

and configurable

Voltage reference module with:- Programmable On-chip Voltage

Reference(CVREF) module (% of VDD)- Selectable on-chip fixed

voltage referencePeripheral Features:

24/35 I/O pins and 1 input-only pin:- High current sink/source

25 mA/25 mA- Individually programmable weak pull-ups-

Individually programmable interrupt-on-pinchange

Three external interrupt pins

Up to seven Timer modules:- Up to four 16-bit timers/counters

with prescaler- Up to three 8-bit timers/counters- Dedicated,

low-power Timer1 oscillator

Up to two Capture/Compare/PWM (CCP) modules

Up to three Enhanced Capture/Compare/PWM(ECCP) modules with:-

One, two or four PWM outputs- Selectable polarity- Programmable

dead time- Auto-shutdown and Auto-restart- PWM output steering

control

Two Master Synchronous Serial Port (MSSP)modules with two modes

of operation:- 3-wire SPI (supports all 4 SPI modes)- I2C™

Master and Slave modes (Slave modewith address masking)

Two Enhanced Universal Synchronous AsynchronousReceiver

Transmitter modules (EUSART):- Supports RS-232, RS-485 and LIN

2.0- Auto-Baud Detect- Auto Wake-up on Start bit.

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone.

High Performance RISC CPU:

C Compiler optimized architecture/instruction set

Data EEPROM to 1024 bytes

Linear program memory addressing to 64 Kbytes

Linear data memory addressing to 4 Kbytes

Up to 16 MIPS operation

16-bit wide instructions, 8-bit wide data path

Priority levels for interrupts

31-level, software accessible hardware stack

8 x 8 Single-Cycle Hardware MultiplierExtreme Low-Power

Managementwith nanoWatt XLP™:

Sleep mode: 100 nA, typical

Watchdog Timer: 500 nA, typical

Timer1 Oscillator: 500 nA @ typical 32 kHzFlexible Oscillator

Structure:

Precision 16 MHz internal oscillator block:- Factory calibrated

to ± 1%- Software selectable frequencies range of31 kHz to 16

MHz- 64 MHz performance available using PLL –no external

components required

Four Crystal modes up to 64 MHz

Two external Clock modes up to 64 MHz

4X Phase Lock Loop (PLL)

Secondary oscillator using Timer1 @ 32 kHz

Fail-Safe Clock Monitor:- Allows for safe shutdown if peripheral

clockstops

Two-Speed Oscillator Start-upSpecial Microcontroller Features:

Full 5.5V operation (PIC18F2XK22/4XK22)

Low voltage option available for 1.8V-3.6V operation

(PIC18LF2XK22/4XK22)

Self-reprogrammable under software control

Power-on Reset (POR), Power-up Timer (PWRT)and Oscillator Start

-up Timer (OST)

Programmable Brown-out Reset (BOR)

Extended Watchdog Timer (WDT) with on-chiposcillator and

software enable

Programmable code protection

In-Circuit Serial Programming™ (ICSP™) viatwo pins

In-Circuit Debug via two pinsAnalog Features:

Analog-to-Digital Converter (ADC) module:- 10-bit resolution- 17

analog input channels (PIC18F/LF2XK22)- 28 analog input channels

(PIC18F/LF4XK22)- Auto acquisition capability- Conversion

available during Sleep

Programmable High/Low Voltage Detection(PLVD) module

Charge Time Measurement Unit (CTMU) formTouch™ support:- Up to

28 channels for button, sensor or sliderinput

Analog comparator module with:- Two rail-to-rail analog

comparators- Comparator inputs and outputs externallyaccessible

and configurable

Voltage reference module with:- Programmable On-chip Voltage

Reference(CVREF) module (% of VDD)- Selectable on-chip fixed

voltage referencePeripheral Features:

24/35 I/O pins and 1 input-only pin:- High current sink/source

25 mA/25 mA- Individually programmable weak pull-ups-

Individually programmable interrupt-on-pinchange

Three external interrupt pins

Up to seven Timer modules:- Up to four 16-bit timers/counters

with prescaler- Up to three 8-bit timers/counters- Dedicated,

low-power Timer1 oscillator

Up to two Capture/Compare/PWM (CCP) modules

Up to three Enhanced Capture/Compare/PWM(ECCP) modules with:-

One, two or four PWM outputs- Selectable polarity- Programmable

dead time- Auto-shutdown and Auto-restart- PWM output steering

control

Two Master Synchronous Serial Port (MSSP)modules with two modes

of operation:- 3-wire SPI (supports all 4 SPI modes)- I2C™

Master and Slave modes (Slave modewith address masking)

Two Enhanced Universal Synchronous AsynchronousReceiver

Transmitter modules (EUSART):- Supports RS-232, RS-485 and LIN

2.0- Auto-Baud Detect- Auto Wake-up on Start bit.

PIC18F13K50 MCU CRACK

PIC18F13K50 MCU CRACK,microchip chip decrypt, chip code

extraction, pic chip crack, pic chip clone, microchip chip

products clone.PCB cLone .

The PIC18F13K50 brings advanced features and exceptional value

to the embedded USB market. This low cost PIC® Microcontroller

features a full speed USB 2.0 compliant interface that can

automatically change clock sources and power levels upon

connection to a host, making it an exceptional device for

battery-powered applications. The addition of mTouch(TM) touch